Giới thiệu

Kiến trúc RISC (Reduced Instruction Set Computer) đã nổi lên như một trong những đột phá quan trọng trong lĩnh vực thiết kế vi xử lý. Được giới thiệu vào những năm 1980, RISC đã chứng minh khả năng vượt trội trong việc tối ưu hóa hiệu suất xử lý và giảm thiểu độ phức tạp, đồng thời mở ra những con đường mới cho sự phát triển công nghệ máy tính. Trong bài viết này, chúng ta sẽ đi sâu vào các khía cạnh lịch sử, kỹ thuật, và ảnh hưởng của kiến trúc RISC, cùng với phân tích các xu hướng và thách thức trong tương lai.

1. Lịch Sử và Nguyên Tắc Cơ Bản

1.1. Bối Cảnh Lịch Sử

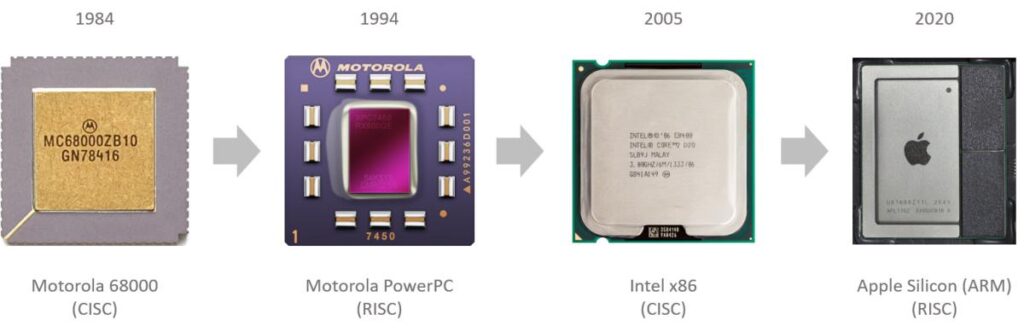

Trước khi kiến trúc RISC ra đời, ngành công nghiệp máy tính chủ yếu dựa vào kiến trúc CISC (Complex Instruction Set Computer). Các vi xử lý CISC, chẳng hạn như Intel 8086 và 6502, sử dụng một tập hợp lệnh phong phú và phức tạp, với mục tiêu thực hiện các tác vụ phức tạp trong một lệnh duy nhất. Tuy nhiên, điều này dẫn đến việc gia tăng độ phức tạp trong thiết kế phần cứng và phần mềm, cũng như giảm hiệu suất do số chu kỳ đồng hồ cần thiết để thực thi mỗi lệnh.

1.2. Nguyên Tắc Thiết Kế RISC

Kiến trúc RISC được phát triển như một giải pháp cho những vấn đề này. Nguyên tắc cơ bản của RISC là đơn giản hóa bộ lệnh để giảm thiểu thời gian giải mã và thực thi. Điều này được thực hiện bằng cách:

- Giảm Số Lượng Lệnh: RISC sử dụng một tập hợp các lệnh cơ bản, dễ hiểu và có độ dài cố định.

- Thực Thi Trong Một Chu Kỳ: Các lệnh được thiết kế để thực thi trong một chu kỳ đồng hồ, giúp giảm độ trễ và cải thiện hiệu suất.

- Sử Dụng Thanh Ghi (Register): Thay vì truy cập bộ nhớ chính thường xuyên, RISC ưu tiên việc sử dụng các thanh ghi, giảm thiểu số lần truy cập bộ nhớ và tối ưu hóa băng thông.

2. Cấu Trúc và Đặc Điểm Kỹ Thuật

2.1. Tập Lệnh Đơn Giản và Đồng Nhất

Các lệnh trong kiến trúc RISC được thiết kế để có độ dài cố định và cấu trúc đơn giản. Điều này giúp việc giải mã lệnh diễn ra nhanh chóng và hiệu quả. Các lệnh cơ bản thường bao gồm các phép toán số học, logic, và các lệnh điều kiện. Việc sử dụng tập lệnh đơn giản giúp giảm thiểu các giai đoạn giải mã và thực thi, từ đó tăng cường hiệu suất tổng thể của vi xử lý.

2.2. Chế Độ Thực Thi Trong Một Chu Kỳ

Một trong những điểm mạnh của RISC là khả năng thực thi hầu hết các lệnh trong một chu kỳ đồng hồ. Để đạt được điều này, thiết kế phần cứng của RISC phải đảm bảo rằng tất cả các giai đoạn của chu trình xử lý được tối ưu hóa và đồng bộ. Điều này đòi hỏi sự cải tiến trong kỹ thuật thiết kế vi xử lý, bao gồm việc sử dụng các kỹ thuật pipeline và các công cụ hỗ trợ khác để giảm thiểu thời gian thực thi.

2.3. Tập Trung Vào Thanh Ghi

Việc sử dụng thanh ghi trong RISC là một điểm khác biệt quan trọng so với CISC. RISC giảm số lượng các phép toán trực tiếp với bộ nhớ chính và thay vào đó, thực hiện các phép toán trong các thanh ghi. Điều này không chỉ giảm thiểu độ trễ trong việc truy cập bộ nhớ mà còn tối ưu hóa việc sử dụng băng thông của hệ thống.

2.4. Kỹ Thuật Pipeline và Superscalar

Kiến trúc RISC hỗ trợ các kỹ thuật pipeline, cho phép xử lý nhiều lệnh đồng thời bằng cách chia nhỏ quá trình thực thi thành các giai đoạn khác nhau. Kỹ thuật này giúp tăng cường hiệu suất bằng cách tận dụng tối đa khả năng xử lý đồng thời của vi xử lý. Hơn nữa, kiến trúc superscalar, một bước tiến từ RISC, cho phép nhiều lệnh được thực thi đồng thời trong một chu kỳ đồng hồ, giúp cải thiện đáng kể hiệu suất của vi xử lý.

3. Ứng Dụng và Tầm Quan Trọng

3.1. Các Thiết Bị Di Động và Nhúng

Kiến trúc RISC, đặc biệt là qua các vi xử lý ARM, đã trở thành tiêu chuẩn trong các thiết bị di động và nhúng. Các vi xử lý ARM cung cấp sự kết hợp giữa hiệu suất cao và tiết kiệm năng lượng, làm cho chúng lý tưởng cho các thiết bị như điện thoại thông minh, máy tính bảng và thiết bị IoT. ARM đã dẫn đầu trong việc cung cấp các giải pháp hiệu quả cho các ứng dụng di động và nhúng, nhờ vào thiết kế đơn giản và khả năng mở rộng linh hoạt của RISC.

3.2. Máy Chủ và Tính Toán Hiệu Suất Cao

Ngoài các ứng dụng di động, kiến trúc RISC cũng được áp dụng trong các máy chủ và hệ thống tính toán hiệu suất cao (HPC). Ví dụ, các vi xử lý dựa trên RISC như IBM POWER đã chứng minh khả năng xử lý song song và tính linh hoạt trong các hệ thống máy chủ, từ đó đáp ứng các yêu cầu khắt khe về hiệu suất và khả năng mở rộng.

4. Xu Hướng và Thách Thức Tương Lai

4.1. Sự Phát Triển của RISC-V

RISC-V, một phiên bản mở của kiến trúc RISC, đang nổi lên như một lựa chọn thay thế mạnh mẽ cho các vi xử lý thương mại. Sự mở rộng và khả năng tùy chỉnh của RISC-V mang lại những lợi ích lớn cho các nhà thiết kế vi xử lý, từ việc tùy chỉnh các lệnh đến việc tối ưu hóa hiệu suất cho các ứng dụng cụ thể. Sự phát triển của RISC-V cũng phản ánh xu hướng ngày càng tăng trong việc tạo ra các giải pháp thiết kế phần cứng mở và linh hoạt.

4.2. Tích Hợp và Tinh Chỉnh

Trong tương lai, việc tích hợp kiến trúc RISC với các công nghệ mới như trí tuệ nhân tạo và học máy sẽ mở ra những khả năng mới. Sự phát triển của các mô hình máy học và trí tuệ nhân tạo đòi hỏi khả năng xử lý song song mạnh mẽ và hiệu suất cao, điều mà RISC có thể cung cấp. Tuy nhiên, việc tích hợp này cũng đòi hỏi các cải tiến trong thiết kế phần cứng để đáp ứng nhu cầu ngày càng cao về hiệu suất và tính linh hoạt.

4.3. Thách Thức trong Thiết Kế

Dù RISC có nhiều ưu điểm, nó cũng đối mặt với một số thách thức trong thiết kế và triển khai. Các nhà thiết kế cần cân nhắc các yếu tố như tiêu thụ năng lượng, hiệu suất trong các ứng dụng cụ thể, và khả năng tích hợp với các công nghệ mới. Sự phát triển của các công nghệ như điện toán lượng tử và mạng máy tính siêu tốc có thể đặt ra những yêu cầu mới đối với kiến trúc vi xử lý, buộc các nhà nghiên cứu và kỹ sư phải tiếp tục đổi mới và tối ưu hóa thiết kế RISC.

5. Ứng Dụng Vector Hóa và Công Cụ Hỗ Trợ

5.1. Hiệu Suất Vector Hóa của RISC-V

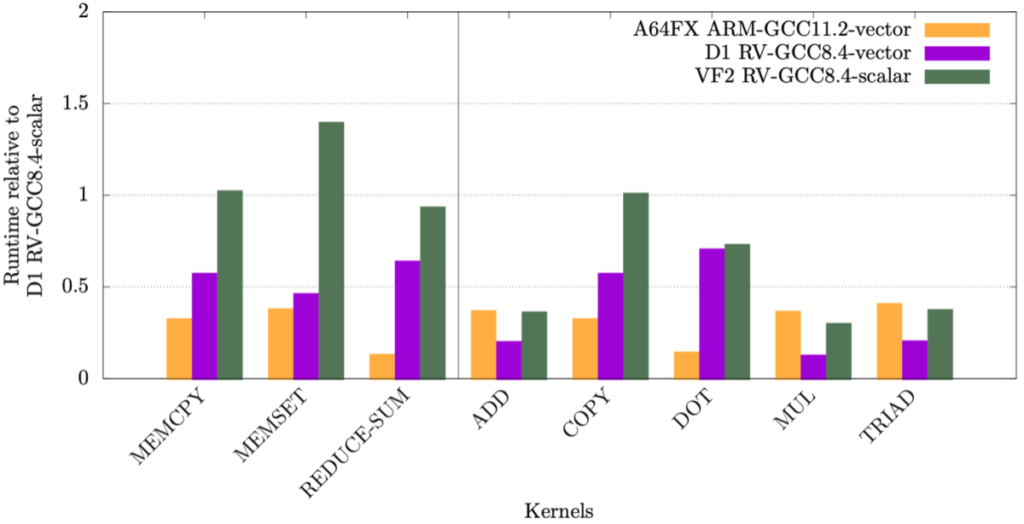

Trong bối cảnh ứng dụng vector hóa, kiến trúc RISC-V đã thể hiện những ưu điểm đáng kể. Hình 3 cho thấy hiệu suất thời gian chạy tương đối của RISC-V với vector hóa so với mã vô hướng. Vector hóa, là quá trình xử lý dữ liệu theo dạng vector để thực hiện nhiều phép toán cùng lúc, giúp cải thiện hiệu suất tính toán đáng kể, đặc biệt trong các ứng dụng yêu cầu xử lý dữ liệu lớn hoặc phức tạp.

5.2. Công Cụ Khôi Phục RVV

Một công cụ quan trọng trong việc tận dụng vector hóa trên nền tảng RISC-V là công cụ khôi phục RVV (RISC-V Vector Extension) v1.0 đến v0.7. Được phát triển bởi Tiến sĩ Joseph Lee như một phần của dự án nền tảng thử nghiệm ExCALIBUR H&ES RISC-V, công cụ này cho phép người dùng chuyển đổi mã nguồn từ định dạng RVV v1.0 sang RVV v0.7. Công cụ này hỗ trợ tự động vector hóa mã bằng cách sử dụng các trình biên dịch GCC và LLVM/Clang chính. Mặc dù vẫn cần sử dụng trình biên dịch XuanTie GCC để lắp ráp các tệp nguồn thành tệp đối tượng hoặc nhị phân, công cụ khôi phục RVV giúp đơn giản hóa quá trình phát triển và triển khai mã vector hóa trên các bo mạch dựa trên Allwinner D1.

**5.3. Nền Tảng

Thử Nghiệm RISC-V**

Nền tảng thử nghiệm RISC-V đã được thiết lập để hỗ trợ các nhà nghiên cứu trong việc kiểm tra mã của họ trên phần cứng RISC-V hiện có. Hiện tại, nền tảng thử nghiệm cung cấp 24 lõi RISC-V trong một cụm slurm, với kế hoạch mở rộng thêm 48 lõi nữa vào tháng 4 và tháng 5 năm 2023, nâng tổng số lõi lên 72. Các nhà nghiên cứu có thể đăng ký để truy cập vào nền tảng thử nghiệm thông qua các bước hướng dẫn trên trang web nền tảng thử nghiệm RISC-V, từ đó thực hiện các thử nghiệm và phân tích sâu hơn về hiệu suất và khả năng của các hệ thống dựa trên RISC-V.

Kết Luận

Sự tiến hóa của kiến trúc RISC không chỉ là một câu chuyện về công nghệ mà còn phản ánh sự đổi mới và sáng tạo trong lĩnh vực thiết kế vi xử lý. Với khả năng cung cấp hiệu suất cao, tiết kiệm năng lượng, và khả năng mở rộng linh hoạt, RISC vẫn tiếp tục là một yếu tố quan trọng trong sự phát triển của ngành công nghiệp máy tính. Việc nghiên cứu và phát triển các phiên bản tiếp theo của RISC, cùng với sự áp dụng trong các lĩnh vực mới và các công cụ hỗ trợ như RVV, sẽ tiếp tục thúc đẩy sự đổi mới trong công nghệ máy tính trong những năm tới.