Chương 1: Giới Thiệu Tổng Quan về FPGA

1.1. Lịch Sử và Phát Triển của FPGA

Khởi nguồn và sự phát triển của FPGA

1.1.1. Khởi Nguyên

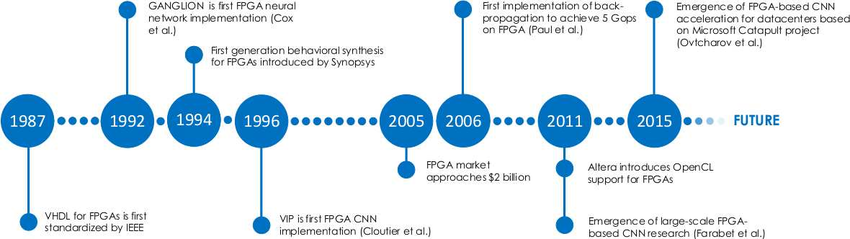

Công nghệ FPGA (Field-Programmable Gate Array) được phát triển lần đầu tiên vào những năm 1980. FPGA là kết quả của nhu cầu về phần cứng có thể lập trình lại để đáp ứng các yêu cầu thay đổi liên tục của các ứng dụng điện tử. Trước khi FPGA ra đời, các thiết kế phần cứng chủ yếu dựa vào các mạch tích hợp ASIC (Application-Specific Integrated Circuit), vốn không thể thay đổi sau khi sản xuất.

- 1985: Xilinx, công ty tiên phong trong ngành FPGA, giới thiệu FPGA đầu tiên của mình, Xilinx XC2064. Sản phẩm này là một bước đột phá trong khả năng lập trình lại phần cứng, cho phép người dùng thiết kế và cấu hình lại mạch tích hợp mà không cần thay đổi phần cứng vật lý.

- 1990s: Sự phát triển của FPGA tiếp tục với các sản phẩm có cấu trúc và hiệu suất ngày càng cải thiện. Các nhà sản xuất như Altera (hiện thuộc Intel) cũng gia nhập thị trường và cạnh tranh với Xilinx, thúc đẩy sự đổi mới và tiến bộ trong công nghệ FPGA.

1.1.2. Các Thế Hệ FPGA

- Thế Hệ Đầu Tiên: FPGA thế hệ đầu tiên có cấu trúc đơn giản với các khối logic cơ bản và khả năng lập trình hạn chế. Chúng chủ yếu được sử dụng trong các ứng dụng thử nghiệm và thiết kế nhỏ.

- Thế Hệ Thứ Hai: Sự xuất hiện của các khối logic phức tạp hơn, bộ nhớ tích hợp, và các công cụ phát triển mạnh mẽ đã mở rộng khả năng của FPGA. Thế hệ này bắt đầu hỗ trợ các ứng dụng phức tạp hơn trong lĩnh vực truyền thông và xử lý tín hiệu.

- Thế Hệ Hiện Tại: Các FPGA thế hệ hiện tại tích hợp hàng triệu logic cells, bộ nhớ mạnh mẽ, và các tính năng xử lý tín hiệu số (DSP) tiên tiến. Chúng hỗ trợ các ứng dụng như trí tuệ nhân tạo (AI), mạng viễn thông 5G, và điện toán biên (edge computing).

Các Mốc Quan Trọng

1.1.3. Các Bước Phát Triển Quan Trọng

- 1990: Xilinx phát hành FPGA Virtex, đánh dấu sự tiến bộ lớn trong công nghệ FPGA với khả năng tích hợp cao hơn và hiệu suất tốt hơn.

- 1995: Altera giới thiệu FPGA FLEX, nổi bật với khả năng tích hợp các khối logic và bộ nhớ trên cùng một chip.

- 2000s: Sự phát triển của các công cụ phát triển và phần mềm hỗ trợ FPGA đã cải thiện khả năng thiết kế và tối ưu hóa cho các ứng dụng phức tạp. Các công ty như Xilinx và Intel (Altera) đã công bố các dòng sản phẩm mới với các tính năng tiên tiến như DSP blocks và các giao tiếp tốc độ cao.

- 2010s: Sự tích hợp của FPGA với các công nghệ khác, chẳng hạn như CPU và GPU, đã mở rộng khả năng ứng dụng của FPGA trong các lĩnh vực như AI và điện toán đám mây.

- 2020s: Các FPGA hiện đại tích hợp các công cụ học máy (machine learning), hỗ trợ các ứng dụng trí tuệ nhân tạo và phân tích dữ liệu lớn với hiệu suất cao.

1.2. Nguyên Lý Hoạt Động Cơ Bản

Cấu trúc cơ bản của FPGA

1.2.1. Các Thành Phần Chính

- Logic Cells: Các khối logic cơ bản trong FPGA, thực hiện các phép toán logic. Logic cells có thể được lập trình để thực hiện các hàm số và thuật toán logic theo yêu cầu của ứng dụng.

- Interconnects: Mạng lưới kết nối cho phép các logic cells và các khối bộ nhớ giao tiếp với nhau. Các interconnects được thiết kế để tối ưu hóa việc truyền tín hiệu và dữ liệu giữa các thành phần của FPGA.

- I/O Blocks: Các khối điều khiển tín hiệu vào và ra, cho phép FPGA giao tiếp với các thiết bị bên ngoài và các hệ thống khác. I/O blocks có thể hỗ trợ nhiều giao thức và chuẩn kết nối khác nhau.

- Memory Blocks: Các vùng bộ nhớ tích hợp cung cấp khả năng lưu trữ dữ liệu tạm thời hoặc cấu hình bộ nhớ theo yêu cầu của ứng dụng.

So sánh với các công nghệ khác

1.2.2. So Sánh với Vi Xử Lý và Vi Điều Khiển

- Vi Xử Lý (Microprocessor): Vi xử lý là phần cứng được lập trình để thực hiện các tác vụ cụ thể và không thể thay đổi sau khi sản xuất. FPGA, ngược lại, có khả năng lập trình lại, cho phép điều chỉnh và cấu hình phần cứng theo nhu cầu. FPGA có khả năng xử lý đồng thời nhiều nhiệm vụ, trong khi vi xử lý thường thực hiện các tác vụ tuần tự.

- Vi Điều Khiển (Microcontroller): Vi điều khiển thường được sử dụng trong các hệ thống nhúng với các ứng dụng điều khiển đơn giản. FPGA có khả năng thực hiện các chức năng phức tạp hơn và có thể cấu hình lại để đáp ứng các yêu cầu thay đổi. Vi điều khiển có cấu trúc cố định và không thể thay đổi, trong khi FPGA cung cấp khả năng linh hoạt cao hơn.

- ASIC (Application-Specific Integrated Circuit): ASIC được thiết kế đặc biệt cho một ứng dụng cụ thể và không thể thay đổi sau khi sản xuất. FPGA, tuy nhiên, cho phép lập trình lại và cấu hình lại, cung cấp khả năng linh hoạt và khả năng thay đổi dễ dàng hơn so với ASIC.

Chương 2: Cấu Trúc Nội Bộ FPGA

2.1. Các Khối Logic (Logic Blocks)

2.1.1. LUT (Look-Up Table)

Khái Niệm và Cách Thức Hoạt Động:

- LUT (Look-Up Table) là một thành phần cơ bản trong FPGA, dùng để thực hiện các phép toán logic. Mỗi LUT có thể lưu trữ một bảng giá trị (lookup table) giúp chuyển đổi đầu vào thành đầu ra dựa trên bảng này.

- Cấu trúc: Một LUT thường được tổ chức dưới dạng bảng với các đầu vào và đầu ra. Ví dụ, một LUT-4 có 4 đầu vào và 16 ô nhớ, mỗi ô lưu trữ một giá trị đầu ra cho một tổ hợp đầu vào cụ thể.

- Chức năng: Khi một giá trị đầu vào được đưa vào, LUT tra cứu giá trị tương ứng từ bảng và xuất kết quả. Điều này cho phép thực hiện các hàm logic phức tạp như AND, OR, XOR, và nhiều hàm logic khác chỉ với một thành phần duy nhất.

Ứng Dụng:

- Thiết kế logic tùy chỉnh: LUT cho phép thiết kế các mạch logic tùy chỉnh mà không cần thiết kế mạch vật lý riêng biệt. Điều này rất hữu ích trong việc triển khai các chức năng logic phức tạp.

- Tối ưu hóa hiệu suất: Sử dụng LUT có thể giảm thiểu số lượng logic cơ bản cần thiết, từ đó cải thiện hiệu suất và tiết kiệm tài nguyên.

2.1.2. FF (Flip-Flop)

Khái Niệm và Vai Trò:

- Flip-Flop (FF) là một thành phần quan trọng trong FPGA, hoạt động như một ô nhớ đồng bộ. Nó lưu trữ trạng thái của dữ liệu và giúp đồng bộ hóa các tín hiệu trong mạch.

- Cấu trúc: Flip-flop thường được điều khiển bởi tín hiệu đồng hồ, và có thể lưu trữ một bit dữ liệu tại một thời điểm. Chúng có thể hoạt động như các latch, D-flip-flop, T-flip-flop, hoặc JK-flip-flop, tùy thuộc vào yêu cầu ứng dụng.

Tương Tác Với Các Khối Logic Khác:

- Lưu trữ và đồng bộ hóa dữ liệu: FF giúp lưu trữ và duy trì dữ liệu trong các khối logic, đảm bảo tính đồng bộ hóa và chính xác trong các phép toán logic.

- Chuyển giao tín hiệu: FF giúp truyền tín hiệu từ một phần của mạch đến phần khác, đồng thời giảm thiểu độ trễ và cải thiện hiệu suất tổng thể.

2.1.3. MUX (Multiplexer)

Khái Niệm và Chức Năng:

- Multiplexer (MUX) là một thành phần quan trọng trong FPGA, dùng để chọn một trong nhiều tín hiệu đầu vào và chuyển tín hiệu đó đến đầu ra.

- Cấu trúc: MUX có nhiều đầu vào và một đầu ra. MUX sử dụng các bit điều khiển để chọn tín hiệu đầu vào cần thiết. Ví dụ, một 4-to-1 MUX có 4 đầu vào, 2 bit điều khiển, và 1 đầu ra.

Ứng Dụng:

- Lựa chọn tín hiệu: MUX cho phép chọn giữa nhiều tín hiệu khác nhau, điều này rất quan trọng trong các thiết kế yêu cầu điều phối tín hiệu linh hoạt.

- Tối ưu hóa mạch: Sử dụng MUX có thể giúp giảm số lượng đường dây cần thiết và cải thiện tổ chức mạch.

2.2. Cấu Trúc Kết Nối (Interconnect Network)

2.2.1. Routing

Khái Niệm và Cơ Chế:

- Routing là cơ chế truyền tín hiệu giữa các khối logic và các thành phần khác trong FPGA. Nó bao gồm các kênh kết nối và các tuyến đường để truyền dữ liệu từ một điểm đến điểm khác.

- Cấu trúc: FPGA sử dụng các mạng lưới dây kết nối và các kênh điều khiển để đảm bảo tín hiệu được truyền đi chính xác và hiệu quả.

Ứng Dụng:

- Định tuyến tín hiệu: Routing giúp xác định cách tín hiệu sẽ được truyền qua FPGA, đảm bảo tính chính xác và tốc độ cao trong các thiết kế.

- Tối ưu hóa: Các công cụ phát triển FPGA sử dụng các thuật toán tối ưu hóa để cải thiện việc routing, giảm thiểu độ trễ và tăng cường hiệu suất.

2.2.2. Switch Matrix

Khái Niệm và Vai Trò:

- Switch Matrix là các ma trận chuyển mạch trong FPGA giúp định tuyến tín hiệu giữa các khối logic và các thành phần khác. Chúng cung cấp khả năng linh hoạt cao trong việc kết nối các thành phần.

- Cấu trúc: Ma trận chuyển mạch bao gồm các công tắc điện tử có thể mở hoặc đóng để điều hướng tín hiệu đến các đường dẫn khác nhau.

Ứng Dụng:

- Tùy chỉnh kết nối: Switch Matrix cho phép tùy chỉnh kết nối giữa các khối logic, giúp thiết kế các mạch phức tạp mà không cần thay đổi phần cứng vật lý.

- Tối ưu hóa tín hiệu: Nó giúp tối ưu hóa việc truyền tín hiệu và giảm thiểu các vấn đề về độ trễ và nhiễu.

2.3. Các Khối Bộ Nhớ (Memory Blocks)

2.3.1. BRAM (Block RAM)

Khái Niệm và Cấu Trúc:

- Block RAM (BRAM) là các khối bộ nhớ tích hợp trong FPGA, cung cấp khả năng lưu trữ dữ liệu với tốc độ cao. Chúng có thể được cấu hình để hoạt động như các bộ nhớ SRAM (Static RAM) hoặc DRAM (Dynamic RAM).

- Cấu trúc: BRAM thường được tổ chức thành các ô nhớ với khả năng đọc và ghi đồng thời. Chúng có thể hỗ trợ nhiều kích cỡ và cấu hình khác nhau.

Ứng Dụng:

- Lưu trữ dữ liệu: BRAM được sử dụng để lưu trữ dữ liệu tạm thời hoặc cấu hình bộ nhớ cho các ứng dụng yêu cầu tốc độ cao.

- Tối ưu hóa hiệu suất: Sử dụng BRAM có thể cải thiện hiệu suất của các ứng dụng yêu cầu bộ nhớ nhanh và hiệu quả.

2.3.2. FIFO (First In, First Out)

Khái Niệm và Cách Thức Hoạt Động:

- FIFO (First In, First Out) là một loại bộ nhớ dùng để quản lý dữ liệu theo thứ tự vào ra. FIFO giúp lưu trữ dữ liệu theo thứ tự mà nó được nhận, với dữ liệu đầu tiên vào sẽ là dữ liệu đầu tiên ra.

- Cấu trúc: FIFO thường bao gồm một hàng đợi dữ liệu với các chỉ số vào và ra, cho phép quản lý và điều phối dữ liệu hiệu quả.

Ứng Dụng:

- Quản lý dữ liệu: FIFO được sử dụng trong các ứng dụng yêu cầu quản lý dữ liệu theo thứ tự, như trong các hệ thống thời gian thực và truyền thông.

- Tối ưu hóa luồng dữ liệu: FIFO giúp cải thiện hiệu suất của các ứng dụng bằng cách quản lý dữ liệu một cách hiệu quả và giảm thiểu độ trễ.

Chương 3: Lập Trình FPGA

3.1. Ngôn Ngữ Mô Tả Phần Cứng (HDL)

3.1.1. VHDL (VHSIC Hardware Description Language)

Khái Niệm và Cấu Trúc:

- VHDL (VHSIC Hardware Description Language) là một ngôn ngữ mô tả phần cứng được phát triển bởi Bộ Quốc phòng Hoa Kỳ trong dự án VHSIC (Very High-Speed Integrated Circuit) vào những năm 1980. VHDL được thiết kế để mô tả, phân tích và thiết kế các hệ thống số.

- Cấu trúc: VHDL có cấu trúc tương tự như các ngôn ngữ lập trình cao cấp với các khối cơ bản như thư viện, package, entity, architecture, và process. Entity định nghĩa giao diện của một phần tử thiết kế, trong khi architecture mô tả cách thức hoạt động bên trong phần tử đó.

- Cú pháp: VHDL có cú pháp mạnh mẽ và chính xác, hỗ trợ cả mô tả hành vi (behavioral modeling) và mô tả cấu trúc (structural modeling). Cú pháp của VHDL yêu cầu việc khai báo kiểu dữ liệu và cấu trúc rõ ràng, điều này giúp giảm lỗi thiết kế và cải thiện khả năng tái sử dụng mã.

Ứng Dụng:

- Thiết kế hệ thống phức tạp: VHDL được sử dụng trong thiết kế các hệ thống số phức tạp như các mạch xử lý tín hiệu số, hệ thống điều khiển và các ứng dụng truyền thông.

- Mô phỏng và kiểm tra: VHDL cung cấp các công cụ mô phỏng mạnh mẽ để kiểm tra các thiết kế trước khi chúng được triển khai vào FPGA.

3.1.2. Verilog

Khái Niệm và Cấu Trúc:

- Verilog là một ngôn ngữ mô tả phần cứng được phát triển vào những năm 1980 bởi Phil Moorby và DesigWorks. Verilog được thiết kế để đơn giản hóa việc mô tả phần cứng và cải thiện quy trình thiết kế phần cứng.

- Cấu trúc: Verilog có cấu trúc với các khối cơ bản như module, always blocks, initial blocks, và tasks/functions. Module là đơn vị cơ bản của thiết kế trong Verilog, tương đương với entity trong VHDL. Always blocks và initial blocks được sử dụng để mô tả hành vi của mạch.

- Cú pháp: Verilog có cú pháp đơn giản và gần gũi với các ngôn ngữ lập trình phần mềm như C. Điều này giúp các kỹ sư phần mềm dễ dàng chuyển sang thiết kế phần cứng bằng Verilog.

So Sánh với VHDL:

- Sự khác biệt về cú pháp: Verilog có cú pháp đơn giản hơn và dễ tiếp cận hơn so với VHDL. VHDL, mặc dù phức tạp hơn, cung cấp khả năng mô tả chi tiết hơn và chính xác hơn.

- Ưu điểm của Verilog: Verilog thường được ưa chuộng trong cộng đồng thiết kế vì cú pháp đơn giản và khả năng mô tả hành vi nhanh chóng. Nó cũng có sự tích hợp tốt với các công cụ mô phỏng và thiết kế phần mềm.

- Ưu điểm của VHDL: VHDL cung cấp khả năng mô tả chi tiết và chính xác hơn, đặc biệt hữu ích cho các thiết kế phức tạp và các ứng dụng yêu cầu tính chính xác cao.

Đoạn mã cơ bản lâp trình FPGA

// Định nghĩa mô-đun bộ đếm nhị phân 4-bit

module binary_counter (

input wire clk, // Đầu vào xung nhịp

input wire reset, // Đầu vào tín hiệu reset

output reg [3:0] count // Đầu ra bộ đếm 4-bit

);

// Quy trình luôn luôn chạy tại mỗi xung nhịp

always @(posedge clk or posedge reset) begin

if (reset) begin

// Khi reset, đặt giá trị bộ đếm về 0

count <= 4'b0000;

end else begin

// Nếu không có tín hiệu reset, tăng giá trị bộ đếm

count <= count + 1;

end

end

endmoduleGiải thích mã:

- module binary_counter: Khai báo mô-đun FPGA với tên là

binary_counter. Đây là phần chính của thiết kế FPGA. - input wire clk, reset: Định nghĩa các tín hiệu đầu vào

clk(xung nhịp) vàreset(tín hiệu reset). - output reg [3:0] count: Định nghĩa đầu ra

countlà một thanh ghi 4-bit. - always @(posedge clk or posedge reset): Khai báo quy trình luôn luôn chạy ở mỗi bờ dương của xung nhịp (

clk) hoặc khi có tín hiệu reset. - if (reset): Nếu có tín hiệu reset, bộ đếm sẽ được đặt về giá trị 0 (

4'b0000). - else: Nếu không có tín hiệu reset, giá trị của bộ đếm sẽ được tăng lên 1.

Đoạn mã này rất cơ bản nhưng cung cấp cái nhìn tổng quan về cách cấu trúc và lập trình FPGA sử dụng Verilog. Bạn có thể mở rộng nó để thực hiện các chức năng phức tạp hơn trong các thiết kế FPGA của mình.

3.2. Công Cụ Phát Triển

3.2.1. Synthesis Tools

Khái Niệm và Quá Trình:

- Synthesis Tools là các công cụ chuyển đổi mã HDL (như VHDL hoặc Verilog) thành cấu hình phần cứng có thể được tải vào FPGA. Quá trình này bao gồm việc chuyển đổi mô tả phần cứng thành các khối logic và kết nối vật lý trên FPGA.

- Quá trình tổng hợp (synthesis): Các công cụ tổng hợp sẽ phân tích mã HDL và chuyển đổi nó thành biểu đồ mạng logic. Quá trình này bao gồm việc phân tích các khối logic, định tuyến tín hiệu, và tối ưu hóa thiết kế để phù hợp với cấu trúc FPGA.

Công Cụ Phát Triển:

- Xilinx Vivado: Một công cụ phổ biến cho việc thiết kế và tổng hợp FPGA, cung cấp khả năng thiết kế đồ họa, phân tích và tối ưu hóa mã HDL.

- Intel Quartus: Công cụ thiết kế FPGA của Intel (trước đây là Altera), hỗ trợ các tính năng tương tự như Vivado với các công cụ tổng hợp và phân tích mạnh mẽ.

3.2.2. Place and Route

Khái Niệm và Kỹ Thuật:

- Place and Route là các kỹ thuật tối ưu hóa trong quá trình thiết kế FPGA, bao gồm việc đặt các khối logic vào các vị trí cụ thể trên FPGA và định tuyến tín hiệu giữa chúng.

- Place (Đặt): Quá trình này bao gồm việc xác định vị trí của các khối logic trên FPGA sao cho tối ưu hóa việc truyền tín hiệu và hiệu suất.

- Route (Định tuyến): Quá trình định tuyến xác định cách thức tín hiệu sẽ được truyền qua các kênh kết nối của FPGA, đảm bảo rằng các tín hiệu được truyền đi một cách chính xác và hiệu quả.

Tối Ưu Hóa:

- Giảm thiểu độ trễ: Kỹ thuật tối ưu hóa trong place and route giúp giảm thiểu độ trễ trong việc truyền tín hiệu và cải thiện hiệu suất tổng thể của thiết kế FPGA.

- Tăng cường hiệu suất: Các công cụ tối ưu hóa cung cấp các giải pháp để cải thiện hiệu suất thiết kế và sử dụng tài nguyên FPGA một cách hiệu quả.

3.2.3. Timing Analysis

Khái Niệm và Quá Trình:

- Timing Analysis là quá trình phân tích thời gian trong thiết kế FPGA để đảm bảo rằng thiết kế đáp ứng các yêu cầu về thời gian và hiệu suất.

- Quá trình phân tích: Phân tích thời gian bao gồm việc kiểm tra các đường tín hiệu và đồng hồ để đảm bảo rằng tất cả các tín hiệu được truyền đi và xử lý trong thời gian quy định. Điều này bao gồm việc đánh giá các chỉ số như tần số đồng hồ, độ trễ, và thời gian trễ.

Công Cụ và Kỹ Thuật:

- Static Timing Analysis (STA): Công cụ phân tích thời gian tĩnh kiểm tra thiết kế FPGA mà không cần mô phỏng, đánh giá các đường tín hiệu và đồng hồ dựa trên các thông số thời gian.

- Timing Constraints: Các ràng buộc thời gian được thiết lập trong thiết kế để đảm bảo rằng tất cả các tín hiệu đáp ứng yêu cầu thời gian và hiệu suất cần thiết.

Chương 4: Ứng Dụng Nâng Cao của FPGA

4.1. Xử Lý Tín Hiệu Số (DSP)

4.1.1. DSP Blocks

Khái Niệm và Tính Năng:

- DSP Blocks (Digital Signal Processing Blocks) là các khối chuyên biệt trong FPGA được thiết kế để xử lý tín hiệu số một cách hiệu quả và nhanh chóng. Các khối này tích hợp các chức năng xử lý tín hiệu như nhân, cộng, và các phép toán số học phức tạp.

- Tính năng: DSP blocks thường bao gồm các bộ nhân đa tầng, bộ cộng, bộ trữ số và các mạch xử lý khác. Chúng được tối ưu hóa cho các phép toán số học và xử lý tín hiệu với tốc độ cao và tiêu thụ năng lượng thấp.

Ứng Dụng:

- Xử lý tín hiệu số: DSP blocks có thể được sử dụng trong các ứng dụng như lọc tín hiệu, phân tích tần số, và biến đổi Fourier. Chúng cung cấp hiệu suất cao cho các phép toán DSP phức tạp mà không làm giảm hiệu suất của các khối logic khác trong FPGA.

- Các ứng dụng cụ thể: DSP blocks có thể được áp dụng trong các hệ thống truyền thông để xử lý tín hiệu vô tuyến, trong các hệ thống âm thanh để lọc và phân tích âm thanh, và trong các hệ thống video để xử lý hình ảnh và video với chất lượng cao.

4.1.2. Các Ví Dụ Ứng Dụng

Xử Lý Âm Thanh:

- Lọc âm thanh: DSP blocks có thể được sử dụng để thiết kế các bộ lọc số cho việc lọc tiếng ồn và cải thiện chất lượng âm thanh. Các ứng dụng bao gồm xử lý tín hiệu âm thanh trong hệ thống hội nghị, âm thanh vòm trong hệ thống giải trí, và các thiết bị nghe nhìn.

- Nhận diện âm thanh: Trong các hệ thống nhận diện giọng nói, DSP blocks giúp phân tích và xử lý các tín hiệu âm thanh để nhận diện từ ngữ và lệnh.

Xử Lý Video:

- Nén video: DSP blocks có thể được sử dụng để thực hiện các thuật toán nén video như H.264 và HEVC, giúp giảm dung lượng video mà vẫn duy trì chất lượng cao.

- Xử lý hình ảnh: Trong các hệ thống xử lý hình ảnh, DSP blocks hỗ trợ các chức năng như phát hiện biên, lọc, và tăng cường độ nét để cải thiện chất lượng hình ảnh.

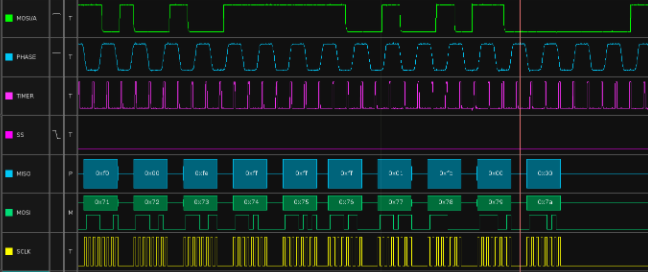

4.2. Giao Tiếp và Đồng Bộ Hóa

4.2.1. Clock Management

Khái Niệm và Công Cụ:

- Clock Management là quá trình quản lý tín hiệu đồng hồ trong FPGA để đảm bảo đồng bộ hóa và hiệu suất chính xác của thiết kế. Nó bao gồm các công cụ và kỹ thuật để tạo, điều chỉnh và phân phối tín hiệu đồng hồ trong FPGA.

- PLL (Phase-Locked Loop): PLL là một công cụ quản lý đồng hồ được sử dụng để tạo ra tín hiệu đồng hồ chính xác từ một tín hiệu đầu vào. PLL có khả năng điều chỉnh tần số và pha của tín hiệu đồng hồ, giúp đồng bộ hóa các phần của thiết kế FPGA.

- DLL (Delay-Locked Loop): DLL là một công cụ tương tự như PLL nhưng tập trung vào việc điều chỉnh độ trễ của tín hiệu đồng hồ. DLL giúp cải thiện độ chính xác của các tín hiệu đồng hồ bằng cách điều chỉnh độ trễ.

Ứng Dụng:

- Đồng bộ hóa: Clock management giúp đảm bảo rằng tất cả các phần của thiết kế FPGA hoạt động đồng bộ với nhau, điều này rất quan trọng trong các hệ thống yêu cầu đồng bộ hóa cao như truyền thông và xử lý tín hiệu.

- Tăng cường hiệu suất: PLL và DLL giúp cải thiện hiệu suất của các hệ thống bằng cách điều chỉnh và quản lý tín hiệu đồng hồ một cách chính xác, giảm thiểu độ trễ và nhiễu.

4.2.2. High-Speed I/O

Khái Niệm và Tính Năng:

- High-Speed I/O là các giao tiếp tốc độ cao được tích hợp trong FPGA để hỗ trợ các ứng dụng yêu cầu băng thông lớn và tốc độ truyền dữ liệu nhanh. Các giao tiếp này bao gồm các chuẩn như LVDS (Low Voltage Differential Signaling), SERDES (Serializer/Deserializer), và các giao tiếp tốc độ cao khác.

- Tính năng: High-speed I/O hỗ trợ tốc độ truyền dữ liệu nhanh, độ chính xác cao và khả năng tương thích với các chuẩn giao tiếp công nghiệp. Chúng được thiết kế để giảm thiểu độ trễ và cải thiện hiệu suất truyền dữ liệu.

Ứng Dụng:

- Hệ thống truyền thông: High-speed I/O được sử dụng trong các hệ thống truyền thông để truyền tải dữ liệu nhanh chóng và hiệu quả. Ví dụ, trong các hệ thống mạng và các thiết bị viễn thông, high-speed I/O hỗ trợ việc truyền tín hiệu số với tốc độ cao và băng thông lớn.

- Ứng dụng xử lý video: Các ứng dụng yêu cầu truyền tải video chất lượng cao và độ phân giải cao sử dụng high-speed I/O để xử lý và truyền tải dữ liệu video mà không làm giảm chất lượng.

Chương 5: FPGA và AI

5.1. Tích Hợp AI vào FPGA

5.1.1. Accelerator for AI

Khái Niệm và Lợi Ích:

- Accelerator for AI: FPGA có thể được sử dụng như các bộ tăng tốc (accelerators) cho các thuật toán học máy (machine learning) và trí tuệ nhân tạo (AI). FPGA cung cấp khả năng tùy chỉnh phần cứng giúp tối ưu hóa các phép toán và cải thiện hiệu suất cho các mô hình AI.

- Tính năng: FPGA có khả năng thực hiện các phép toán song song, điều này rất quan trọng trong việc xử lý các mạng nơ-ron sâu (deep neural networks) và các mô hình học máy phức tạp. FPGA cho phép tối ưu hóa các phép toán như ma trận nhân, tích chập (convolution), và phân loại với hiệu suất cao.

Cách FPGA Tăng Tốc Các Thuật Toán AI:

- Tối ưu hóa phần cứng: FPGA có thể được cấu hình để thực hiện các phép toán AI với hiệu suất cao bằng cách sử dụng các khối logic và DSP blocks. Điều này giúp giảm thiểu thời gian tính toán và tiêu thụ năng lượng so với các giải pháp phần cứng truyền thống như CPU và GPU.

- Tích hợp mô hình: FPGA có thể được cấu hình để tích hợp trực tiếp các mô hình AI, giúp cải thiện hiệu suất và giảm thiểu độ trễ trong các ứng dụng AI. Việc này bao gồm việc triển khai các mạng nơ-ron, thuật toán học sâu, và các ứng dụng AI phức tạp khác.

5.1.2. AI Frameworks

Khái Niệm và Công Cụ:

- AI Frameworks: Các công cụ và framework hỗ trợ việc tích hợp AI vào FPGA giúp đơn giản hóa quá trình thiết kế và triển khai các ứng dụng AI trên FPGA. Các công cụ này cung cấp các API, thư viện, và công cụ phát triển để dễ dàng triển khai các mô hình học máy trên FPGA.

- Các công cụ phổ biến: Một số công cụ và framework hỗ trợ tích hợp AI vào FPGA bao gồm:

- Xilinx Vitis AI: Một framework phát triển phần mềm của Xilinx cho phép các nhà phát triển dễ dàng triển khai các mô hình học máy trên FPGA.

- Intel OpenVINO: Một toolkit của Intel giúp chuyển đổi và tối ưu hóa các mô hình học máy để chạy trên FPGA và các thiết bị AI khác.

- TensorFlow Lite for Microcontrollers: Một phiên bản nhẹ của TensorFlow dành cho các thiết bị nhúng, bao gồm FPGA, để triển khai các mô hình học máy.

Ứng Dụng:

- Tạo môi trường phát triển: Các framework giúp tạo ra môi trường phát triển thuận lợi cho việc thiết kế và tối ưu hóa các ứng dụng AI trên FPGA, từ việc chuyển đổi mô hình đến tối ưu hóa phần cứng.

- Tăng cường hiệu suất: Các công cụ này cung cấp các tính năng tối ưu hóa và hỗ trợ phần cứng, giúp cải thiện hiệu suất và giảm thiểu độ trễ trong các ứng dụng AI.

5.2. Các Ví Dụ Ứng Dụng

5.2.1. Nhận Dạng Hình Ảnh

Ứng Dụng và Lợi Ích:

- Nhận diện hình ảnh và video: FPGA được sử dụng trong các ứng dụng nhận diện hình ảnh và video để xử lý và phân tích dữ liệu hình ảnh với tốc độ cao và hiệu suất cao. Các ứng dụng này bao gồm nhận diện khuôn mặt, phân loại đối tượng, và phát hiện chuyển động.

- Tính năng: FPGA có khả năng xử lý các thuật toán phân tích hình ảnh phức tạp, như các mạng nơ-ron tích chập (CNN) và các mô hình học sâu khác, với hiệu suất cao và tiêu thụ năng lượng thấp.

Ví Dụ Ứng Dụng:

- Hệ thống giám sát: Trong các hệ thống giám sát video, FPGA giúp xử lý và phân tích hình ảnh theo thời gian thực, giúp nhận diện và cảnh báo các sự kiện quan trọng.

- Thiết bị y tế: FPGA có thể được sử dụng trong các thiết bị y tế để phân tích hình ảnh y khoa như MRI và CT scan, giúp hỗ trợ chẩn đoán và điều trị.

5.2.2. Phân Tích Dữ Liệu Lớn

Khái Niệm và Ứng Dụng:

- Phân tích dữ liệu lớn: FPGA hỗ trợ phân tích dữ liệu lớn bằng cách xử lý và phân tích lượng dữ liệu khổng lồ với tốc độ cao và hiệu suất tốt. Các ứng dụng này bao gồm phân tích dữ liệu thời gian thực và xử lý dữ liệu trong các hệ thống lưu trữ dữ liệu lớn.

- Tính năng: FPGA có khả năng thực hiện các phép toán song song, giúp tăng cường khả năng phân tích dữ liệu và xử lý các tác vụ phức tạp nhanh chóng và hiệu quả.

Ví Dụ Ứng Dụng:

- Hệ thống tài chính: Trong các hệ thống tài chính, FPGA giúp phân tích dữ liệu giao dịch và dự đoán xu hướng thị trường với tốc độ cao, hỗ trợ các quyết định giao dịch nhanh chóng.

- Khoa học dữ liệu: FPGA có thể được sử dụng trong các dự án khoa học dữ liệu để xử lý và phân tích các tập dữ liệu lớn, giúp nghiên cứu và phát triển các mô hình học máy và trí tuệ nhân tạo.

Chương 6: Các Xu Hướng và Tiến Bộ Mới trong FPGA

6.1. Công Nghệ Tích Hợp Cao

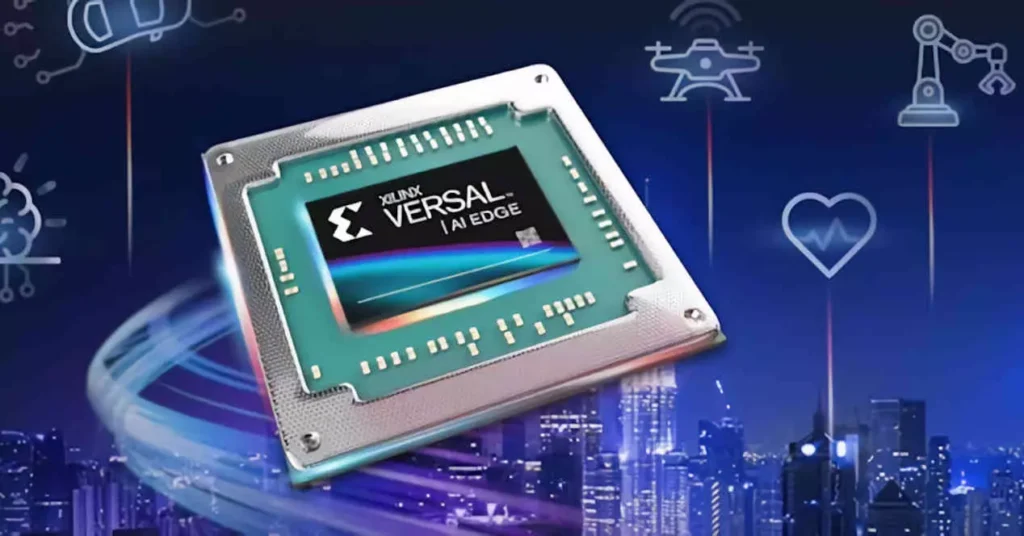

6.1.1. Tích Hợp CPU/GPU

Khái Niệm và Lợi Ích:

- Tích hợp CPU/GPU: Một xu hướng mới trong công nghệ FPGA là tích hợp CPU và GPU trực tiếp vào FPGA, tạo ra các hệ thống đa dạng với khả năng xử lý mạnh mẽ và linh hoạt. Các FPGA tích hợp CPU/GPU cung cấp khả năng xử lý tổng hợp và chuyên biệt cho các ứng dụng yêu cầu hiệu suất cao.

- Lợi ích: Việc tích hợp CPU và GPU vào FPGA cho phép kết hợp khả năng xử lý song song của GPU với khả năng linh hoạt và cấu hình của FPGA. Điều này giúp cải thiện hiệu suất và giảm thiểu độ trễ trong các ứng dụng yêu cầu xử lý phức tạp và tính toán nhanh chóng.

Ứng Dụng:

- Hệ thống nhúng: Các hệ thống nhúng có thể sử dụng FPGA tích hợp CPU/GPU để thực hiện các nhiệm vụ tính toán phức tạp, như xử lý hình ảnh, phân tích dữ liệu và các ứng dụng trí tuệ nhân tạo.

- Thiết bị viễn thông: Trong các thiết bị viễn thông, FPGA tích hợp CPU/GPU có thể được sử dụng để xử lý tín hiệu số và quản lý dữ liệu với tốc độ cao, giúp cải thiện hiệu suất và giảm thiểu độ trễ.

6.1.2. Giao Diện Kết Nối Mới

Khái Niệm và Công Nghệ:

- PCIe (Peripheral Component Interconnect Express): PCIe là một chuẩn giao diện kết nối tốc độ cao được sử dụng để kết nối các thành phần phần cứng với tốc độ truyền dữ liệu nhanh. FPGA hỗ trợ giao diện PCIe để tăng cường khả năng kết nối và truyền dữ liệu trong các hệ thống máy tính.

- Ethernet: Ethernet là một công nghệ mạng phổ biến được sử dụng để kết nối các thiết bị trong mạng cục bộ và mạng diện rộng. Các FPGA hỗ trợ giao diện Ethernet để cung cấp khả năng kết nối mạng tốc độ cao và khả năng truyền dữ liệu lớn.

Ứng Dụng:

- Máy chủ và hệ thống lưu trữ: Các hệ thống máy chủ và lưu trữ sử dụng giao diện PCIe và Ethernet để kết nối các thiết bị và truyền dữ liệu nhanh chóng, giúp cải thiện hiệu suất và khả năng mở rộng.

- Hệ thống mạng: FPGA với giao diện Ethernet hỗ trợ các ứng dụng mạng như chuyển mạch, định tuyến và xử lý dữ liệu mạng, giúp tăng cường hiệu suất và khả năng mở rộng của các hệ thống mạng.

6.2. Đổi Mới và Tinh Chỉnh

6.2.1. Nâng Cao Khả Năng Tinh Chỉnh

Khái Niệm và Công Nghệ:

- Khả năng tinh chỉnh (fine-tuning): Các công nghệ mới trong FPGA giúp cải thiện khả năng tinh chỉnh và cấu hình phần cứng, cho phép các nhà thiết kế tối ưu hóa các thiết kế FPGA để đáp ứng các yêu cầu cụ thể của ứng dụng.

- Công nghệ mới: Các công nghệ mới bao gồm các công cụ phát triển phần mềm nâng cao, các kỹ thuật tối ưu hóa phần cứng và các thuật toán tinh chỉnh giúp cải thiện khả năng tinh chỉnh và hiệu suất của FPGA.

Ứng Dụng:

- Tinh chỉnh thiết kế: Khả năng tinh chỉnh cải thiện việc tối ưu hóa thiết kế FPGA, từ việc điều chỉnh cấu hình phần cứng đến tối ưu hóa hiệu suất và tiêu thụ năng lượng.

- Phát triển sản phẩm: Các công nghệ tinh chỉnh giúp các nhà phát triển tạo ra các sản phẩm FPGA có hiệu suất cao và linh hoạt hơn, đáp ứng các yêu cầu ngày càng cao của các ứng dụng hiện đại.

6.2.2. Tối Ưu Hóa Phần Mềm và Phần Cứng

Khái Niệm và Kỹ Thuật:

- Tối ưu hóa thiết kế phần mềm: Các công cụ và kỹ thuật tối ưu hóa thiết kế FPGA giúp cải thiện hiệu suất của phần mềm và phần cứng, bao gồm việc sử dụng các thuật toán tối ưu hóa, công cụ phân tích và các kỹ thuật tối ưu hóa mã.

- Tối ưu hóa phần cứng: Tối ưu hóa phần cứng bao gồm việc cải thiện cấu trúc FPGA, tối ưu hóa việc sử dụng tài nguyên và giảm thiểu độ trễ. Các công cụ phát triển phần cứng cung cấp các giải pháp để tối ưu hóa thiết kế và cải thiện hiệu suất.

Ứng Dụng:

- Thiết kế phần mềm: Các công cụ tối ưu hóa giúp cải thiện hiệu suất và độ tin cậy của các ứng dụng FPGA, từ việc tối ưu hóa mã đến cải thiện khả năng tương thích với các phần cứng khác.

- Cải thiện hiệu suất hệ thống: Tối ưu hóa phần cứng giúp giảm thiểu độ trễ, tiêu thụ năng lượng và tăng cường hiệu suất tổng thể của các hệ thống FPGA, từ các ứng dụng nhúng đến các hệ thống truyền thông.

Chương 7: Các Thách Thức và Hướng Phát Triển Tương Lai

7.1. Thách Thức Trong Thiết Kế FPGA

7.1.1. Khó Khăn Trong Lập Trình

Phức Tạp Trong Lập Trình:

- Lập trình phần cứng: Lập trình FPGA yêu cầu kiến thức về các ngôn ngữ mô tả phần cứng (HDL) như VHDL hoặc Verilog, và việc học và sử dụng các ngôn ngữ này có thể là một thách thức lớn đối với nhiều nhà phát triển.

- Thiết kế phức tạp: Thiết kế FPGA có thể trở nên phức tạp khi tích hợp nhiều khối chức năng và tối ưu hóa hiệu suất. Việc đảm bảo rằng tất cả các phần của thiết kế hoạt động đồng bộ và hiệu quả là một nhiệm vụ khó khăn.

Công Cụ Phát Triển:

- Hạn chế của công cụ phát triển: Mặc dù có nhiều công cụ phát triển FPGA, nhưng chúng thường có giới hạn về tính năng và khả năng hỗ trợ, điều này có thể gây khó khăn cho việc tối ưu hóa và kiểm tra thiết kế.

- Quá trình kiểm tra và xác nhận: Quá trình kiểm tra và xác nhận thiết kế FPGA có thể phức tạp và tốn thời gian, yêu cầu các kỹ thuật và công cụ đặc biệt để đảm bảo tính chính xác và hiệu suất của thiết kế.

7.1.2. Chi Phí và Hiệu Suất

Chi Phí:

- Chi phí phát triển: Việc phát triển và triển khai các thiết kế FPGA có thể đòi hỏi đầu tư lớn vào phần cứng và phần mềm, đặc biệt là đối với các hệ thống phức tạp hoặc quy mô lớn.

- Chi phí sản xuất: Chi phí sản xuất FPGA cũng có thể cao, đặc biệt là đối với các thiết kế tùy chỉnh hoặc các ứng dụng yêu cầu sản lượng thấp.

Hiệu Suất:

- Hiệu suất so với giải pháp khác: Mặc dù FPGA cung cấp khả năng tùy chỉnh cao và hiệu suất tốt, nhưng trong một số trường hợp, các giải pháp phần cứng khác như GPU hoặc ASIC có thể cung cấp hiệu suất tốt hơn với chi phí thấp hơn.

- Tối ưu hóa hiệu suất: Để đạt được hiệu suất tối ưu, các nhà phát triển phải liên tục tối ưu hóa thiết kế FPGA, điều này có thể yêu cầu sự cân nhắc kỹ lưỡng giữa hiệu suất, chi phí và thời gian phát triển.

7.2. Hướng Phát Triển Tương Lai

7.2.1. Công Nghệ Mới

Công Nghệ 5G và 6G:

- Tích hợp trong mạng 5G/6G: FPGA sẽ đóng vai trò quan trọng trong việc triển khai và tối ưu hóa các mạng 5G và 6G, nhờ khả năng xử lý tín hiệu linh hoạt và hiệu suất cao. FPGA có thể giúp tăng cường khả năng xử lý tín hiệu và quản lý băng thông trong các hệ thống mạng tốc độ cao.

Công Nghệ Quantum Computing:

- Tích hợp với máy tính lượng tử: FPGA có thể được sử dụng để tích hợp và hỗ trợ các máy tính lượng tử, cung cấp các chức năng như giao tiếp, điều khiển và tối ưu hóa các thuật toán lượng tử.

AI và Machine Learning:

- Tích hợp AI: Các công nghệ mới trong AI và học máy sẽ tiếp tục ảnh hưởng đến FPGA, giúp cải thiện khả năng xử lý và tăng cường hiệu suất cho các ứng dụng học máy và trí tuệ nhân tạo.

7.2.2. Ứng Dụng Tương Lai

Ứng Dụng Trong IoT:

- Các thiết bị IoT: FPGA sẽ ngày càng được sử dụng trong các thiết bị IoT để cung cấp khả năng xử lý nhanh chóng và hiệu quả trong các ứng dụng nhúng, giám sát và điều khiển từ xa.

Ngành Y Tế:

- Thiết bị y tế: FPGA có tiềm năng lớn trong ngành y tế, bao gồm việc cải thiện thiết bị chẩn đoán, hỗ trợ xử lý hình ảnh y khoa và phát triển các thiết bị đeo được.

Giao Thông và Tự Động Hóa:

- Hệ thống tự động hóa: FPGA sẽ được sử dụng nhiều hơn trong các hệ thống tự động hóa và giao thông để hỗ trợ các chức năng như điều khiển xe tự hành, quản lý giao thông và cải thiện hiệu suất của các hệ thống điều khiển.