NGUYÊN LÝ HOẠT ĐỘNG CỦA FLIP FLOP JK

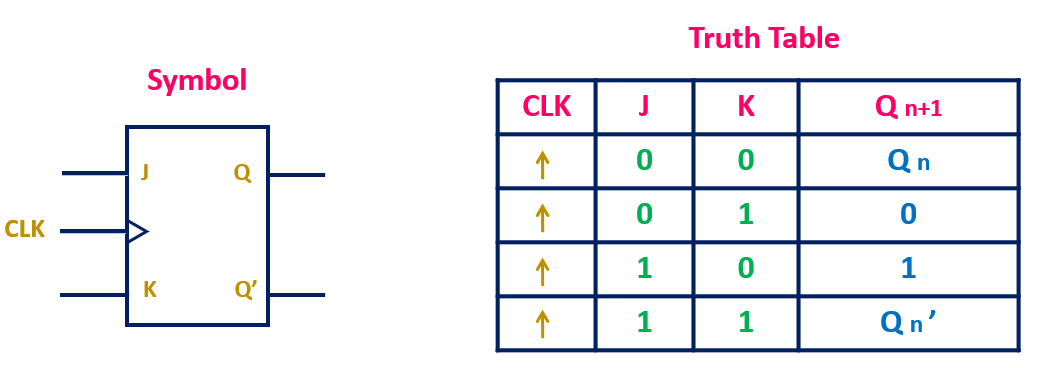

- Flip-flop JK là một mạch lưu trữ bật/tắt tương tự như flip-flop D, tuy nhiên nó có thêm hai đầu vào “J” và “K” để kiểm soát trạng thái đầu ra. Khi “J” và “K” cùng bằng 1, trạng thái của flip-flop sẽ chuyển đổi (từ 0 sang 1 hoặc từ 1 sang 0), nếu không thì trạng thái sẽ được giữ nguyên.

- Khi J=0 và K=0: Trạng thái của Flip-flop JK sẽ được giữ nguyên, nghĩa là đầu ra sẽ không thay đổi.

- Khi J=0 và K=1: Flip-flop JK sẽ bị “tắt” và đầu ra sẽ là 0.

- Khi J=1 và K=0: Flip-flop JK sẽ bị “bật” và đầu ra sẽ là 1.

- Khi J=1 và K=1: Trạng thái của Flip-flop JK sẽ được chuyển đổi, nghĩa là nếu trạng thái hiện tại là 0 thì đầu ra sẽ chuyển sang 1 và ngược lại nếu trạng thái hiện tại là 1 thì đầu ra sẽ chuyển sang 0.

- Trong một số Flip-flop JK, có thể có thêm đầu vào là “CLK” (Clock) để đồng bộ hoạt động với một tín hiệu xung nhất định. Khi đầu vào CLK được kích hoạt (ví dụ như lên xung tín hiệu), Flip-flop JK sẽ cập nhật trạng thái mới dựa trên trạng thái của các đầu vào J, K. Nếu CLK không được kích hoạt, trạng thái của Flip-flop JK sẽ không thay đổi.

- Flip-flop JK có thể được sử dụng trong các ứng dụng như bộ đếm, máy tính, các mạch lưu trữ và các mạch kích thích tín hiệu.

ƯU ĐIỂM CỦA FLIP-FLOP JK

- Điều khiển trạng thái đầu ra: Flip-flop JK có thể điều khiển trạng thái đầu ra bằng cách sử dụng đầu vào J và K, do đó nó rất hữu ích trong các ứng dụng điều khiển và chuyển đổi trạng thái.

- Khả năng đồng bộ: Một số phiên bản Flip-flop JK có thể được điều khiển bởi một tín hiệu xung (CLK), giúp đồng bộ hoạt động của nhiều Flip-flop JK và các mạch khác nhau.

- Tính linh hoạt: Flip-flop JK có thể được sử dụng để thực hiện các chức năng lưu trữ, đếm, chuyển đổi trạng thái và các ứng dụng điều khiển khác, do đó nó rất linh hoạt trong việc thiết kế mạch điện.

- Tương thích với các loại Flip-flop khác: Flip-flop JK có thể được sử dụng để thay thế hoặc kết hợp với các loại Flip-flop khác, như Flip-flop D hay Flip-flop T.

- Thiết kế đơn giản: Flip-flop JK có thiết kế đơn giản, dễ hiểu và dễ sử dụng trong các ứng dụng mạch điện tử.

=> Vì vậy Flip-flop JK là một trong những loại Flip-flop phổ biến được sử dụng trong nhiều ứng dụng điện tử khác nhau.

NHƯỢC ĐIỂM CỦA FLIP-FLOP JK

- Độ trễ: Flip-flop JK có độ trễ nhất định trong quá trình chuyển đổi trạng thái, điều này có thể ảnh hưởng đến thời gian phản hồi của mạch điện tử.

- Số lượng đầu vào: Flip-flop JK có hai đầu vào J và K, do đó nó sẽ chiếm nhiều chân của vi mạch so với một số loại Flip-flop khác chỉ có một hoặc hai đầu vào.

- Độ phức tạp: Trong một số ứng dụng phức tạp, Flip-flop JK có thể không đáp ứng được yêu cầu của thiết kế, và các loại Flip-flop khác sẽ được sử dụng thay thế.

- Suy giảm tín hiệu: Khi tín hiệu vào J và K thay đổi quá nhanh hoặc quá yếu, có thể dẫn đến suy giảm tín hiệu và gây ra sai sót trong trạng thái đầu ra.

ỨNG DỤNG CƠ BẢN CỦA FLIP-FLOP JK

Flip-flop JK là một loại Flip-flop rất phổ biến và có nhiều ứng dụng trong các mạch điện tử số. Dưới đây là một số ứng dụng cơ bản của Flip-flop JK:

- Lưu trữ thông tin: Flip-flop JK được sử dụng để lưu trữ thông tin trong các mạch đếm, mạch tính toán, và các hệ thống điều khiển.

- Chuyển đổi tín hiệu: Flip-flop JK cũng được sử dụng để chuyển đổi tín hiệu từ một dạng sang một dạng khác. Ví dụ, nếu tín hiệu đầu vào là tín hiệu xung, Flip-flop JK có thể được sử dụng để chuyển đổi tín hiệu xung này sang tín hiệu đồng mức.

- Xác định trạng thái: Flip-flop JK cũng được sử dụng để xác định trạng thái trong các hệ thống điều khiển và đo lường. Ví dụ, nếu một cảm biến phát hiện một sự kiện nào đó, Flip-flop JK có thể được sử dụng để lưu trữ trạng thái của sự kiện này và đưa ra quyết định tiếp theo.

- Tạo đồng hồ tín hiệu: Flip-flop JK cũng có thể được sử dụng để tạo ra tín hiệu xung, đây là một tín hiệu xung cơ bản được sử dụng trong rất nhiều ứng dụng điện tử số.

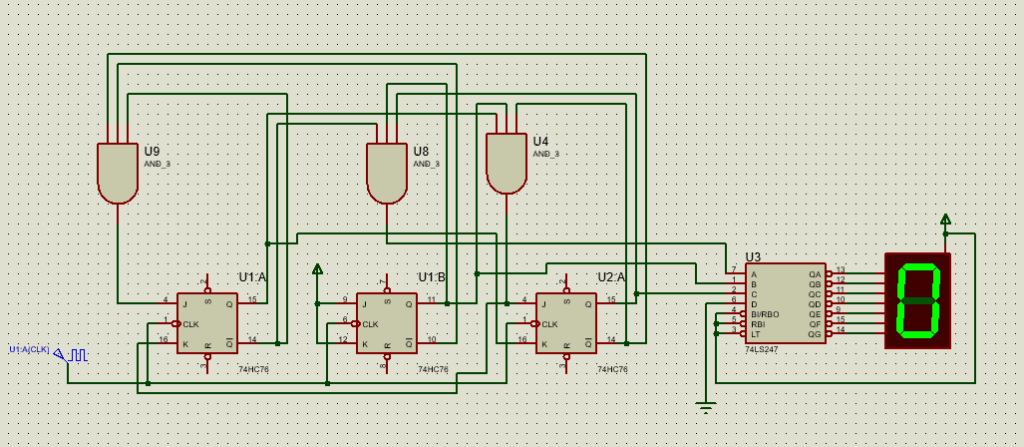

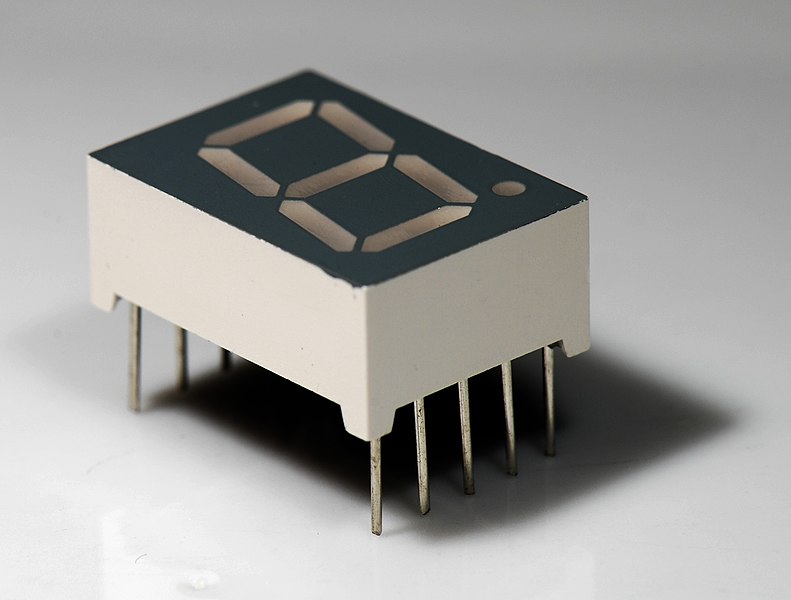

THIẾT KẾ MẠCH ĐẾM

Mạch đếm đồng bộ là một loại mạch đếm có khả năng làm cho tất cả các đầu ra thay đổi trạng thái đồng thời, không có hiện tượng gợn sóng. Điều này đối lập với mạch đếm không đồng bộ.

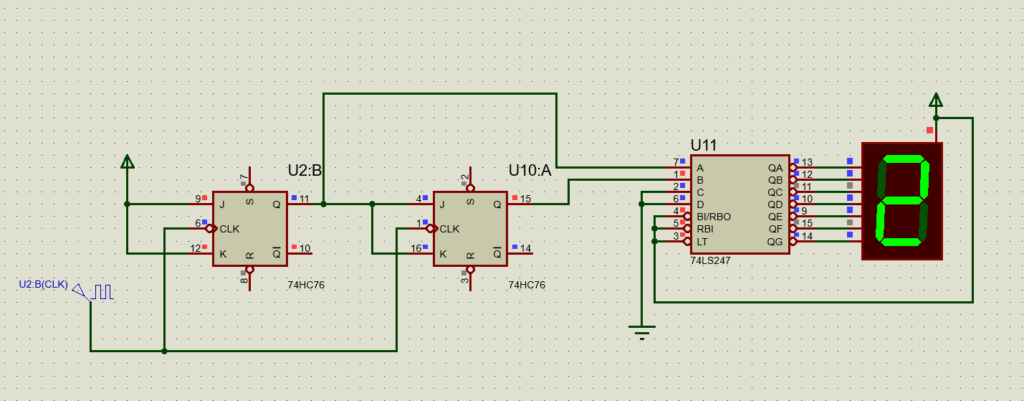

Để tạo được một mạch đếm đồng bộ từ flip-flop J-K, chúng ta cần kết nối tất cả các đầu vào đồng hồ với nhau, để mỗi flip-flop nhận được cùng một xung đồng hồ chính xác tại cùng một thời điểm.

Tuy nhiên, chúng ta cũng cần quan tâm đến đầu vào J và K. Đầu vào này phải ở mức “cao” cùng một thời điểm để đạt được mẫu tần số chia đều trong chuỗi đếm nhị phân. Điều này đảm bảo mạch của chúng ta hoạt động tốt nhất.

Mạch đếm đồng bộ được chia thành 2 kiểu: Mạch đếm lên đồng bộ và mạch đếm xuống đồng bộ. Ở bài viết này chúng ta sẽ thử làm 1 bài liên quan đến mạch đếm lên đồng bộ và 1 mạch đếm không đồng bộ.

MẠCH ĐẾM LÊN ĐỒNG BỘ

Sử dụng Flip flop J-K thiết kế và mô phỏng trên phần mềm Proteus mạch đếm thuận 2 bit với Kđ = 4, chu trình là 0 -> 1 -> 2 -> 3.

Sử dụng Flip flop J-K thiết kế và mô phỏng trên phầm mềm Proteus mạch đếm không đồng bộvới chu trình 0 ->3-> 4 -> 6.